# Western Michigan University ScholarWorks at WMU

Masters Theses

Graduate College

4-2000

# A CMOS Chaotic Oscillator

Boonsin Chansilp Western Michigan University

Follow this and additional works at: https://scholarworks.wmich.edu/masters\_theses

Part of the Electrical and Computer Engineering Commons

## **Recommended Citation**

Chansilp, Boonsin, "A CMOS Chaotic Oscillator" (2000). *Masters Theses*. 4850. https://scholarworks.wmich.edu/masters\_theses/4850

This Masters Thesis-Open Access is brought to you for free and open access by the Graduate College at ScholarWorks at WMU. It has been accepted for inclusion in Masters Theses by an authorized administrator of ScholarWorks at WMU. For more information, please contact wmuscholarworks@wmich.edu.

## A CMOS CHAOTIC OSCILLATOR

by

Boonsin Chansilp

A Thesis Submitted to the Faculty of The Graduate College in partial fulfillment of the requirements for the Degree of Master of Science in Engineering Department of Electrical and Computer Engineering

> Western Michigan University Kalamazoo, Michigan April 2000

Copyright by Boonsin Chansilp 2000

## ACKNOWLEDGMENTS

First of all, I would like to thank Dr. Damon A. Miller, my advisor, who gave me advice and support. His methodical approach in guiding me for concept and trouble shooting helped me to yield better results. Besides being an excellent advisor, he has been a great source of help both as a person and as a teacher.

I thank Dr. Frank L. Severance who gave me more than a teacher. His valuable suggestions during my work lead to a better work. I sincerely thank for his guidance throughout the work.

I am grateful to Dave Florida and John Trucker who support software and hardware during the experiments. My work would never progress without his valuable and kindness.

I would like to thank Dr. Hossein Mousavineshad and Dr. John Gesink for consenting to be on my thesis committee and providing their feedback on my thesis.

Lastly, I would like to thank my family for giving me power and spirit and encouraging me to complete their thesis successfully.

Boonsin Chansilp

#### A CMOS CHAOTIC OSCILLATOR

Boonsin Chansilp, M.S.E.

#### Western Michigan University, 2000

A chaotic oscillator may be used as the basic component of an associative memory (AM). An AM is capable of pattern separation and noise reduction. Chua's circuit is a widely used chaotic oscillator. This circuit consists of a nonlinear resistor, two capacitors, an inductor and a resistor. A discrete implementation of Chua's circuit may be built using operational amplifiers, resistors, diodes, or discrete bipolar transistors. CMOS integrated circuit technology provides the opportunity for a compact implementation which enables construction of systems requiring a large number of oscillators. This thesis develops an integrated circuit design based on previous work performed by Cruz et. al. (1993).

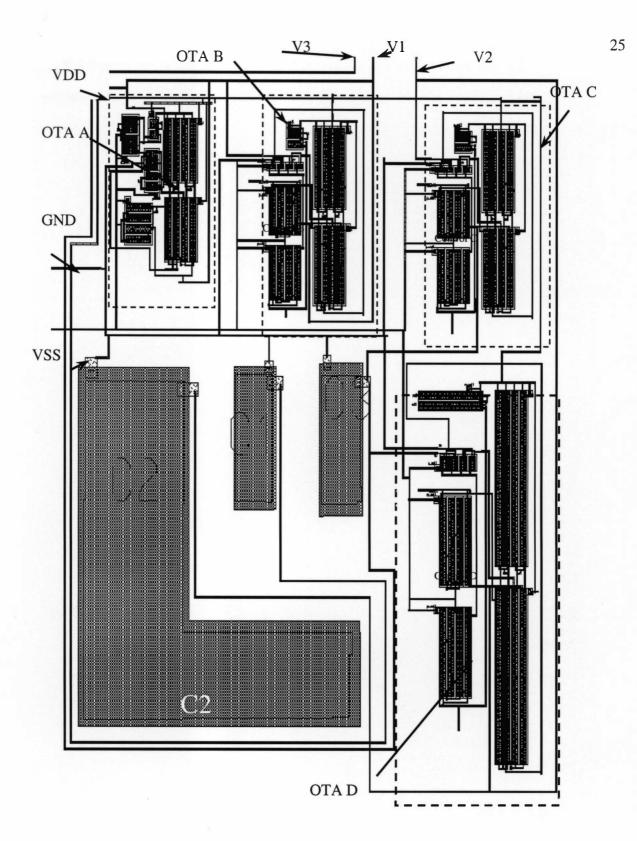

The IC chip has been designed using a  $2 \mu$  m CMOS process. The IC consists of four operational transconductance amplifiers (OTAs), a resistor and three capacitors. The first two OTAs operate as Chua's diode (Cruz 1993) and the other two OTAs in conjunction with the third capacitor realize an inductor. The design process initially used the Spice3f4 circuit simulation package. The final design used Mentor Graphics for simulation, physical layout, Design Rule Checks (DRC), Layout Versus Schematic checks (LVS) and parasitic extraction. All data files as required by fabrication via the MOSIS service were generated.

# TABLE OF CONTENTS

| ACKNOWLEDGMENTS                                       | ii |

|-------------------------------------------------------|----|

| LIST OF TABLES                                        | v  |

| LIST OF FIGURES                                       | vi |

| CHAPTER                                               |    |

| I. INTRODUCTION                                       | 1  |

| Associative Memory                                    | 1  |

| Chua's Circuit: An Easily Realized Chaotic Oscillator | 3  |

| Description                                           | 3  |

| Simulation of Circuit Differential Equations          | 5  |

| II. CIRCUIT DESIGN                                    | 10 |

| Nonlinear Resistor                                    | 10 |

| OTA Design                                            | 12 |

| Gyrator                                               | 14 |

| III. CIRCUIT SIMULATION, LAYOUT AND VERIFICATION      | 16 |

| Circuit Simulation                                    | 16 |

| Layout and Parasitic Extraction                       | 22 |

| Verification                                          | 24 |

| Chip Architecture                                     | 24 |

| IV. CONCLUSION AND FUTURE WORK                        | 31 |

| REFERENCES                                            | 32 |

## Table of Contents—continued

## APPENDICES

| Α.    | Mathematica Code              | 33 |

|-------|-------------------------------|----|

| B.    | Spice Model                   | 38 |

| C.    | How to Use Mentor Graphics    | 44 |

| D.    | Technological Data From MOSIS | 76 |

| BIBLI | OGRAPHY                       | 81 |

## LIST OF TABLES

| 1. | Technological Data     | 16 |

|----|------------------------|----|

| 2. | Mask Device Dimensions | 17 |

## LIST OF FIGURES

| 1.  | Two Cases of AM Recall Demonstrating Noise Reduction and Pattern                                                                                             |    |

|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

|     | Separation                                                                                                                                                   | 1  |

| 2.  | Block Diagram of a Simple Associative Memory                                                                                                                 | 2  |

| 3.  | Chua's Circuit                                                                                                                                               | 4  |

| 4.  | Driving –Point Characteristic of the Nonlinear Resistor                                                                                                      | 5  |

| 5.  | Computation of DC Operating Point                                                                                                                            | 6  |

| 6.  | Chaotic Signal Generated by Chua's Circuit (Mathematica Simulation):<br>(a) $V_1$ , (b) $V_2$ , and (c) <i>i</i>                                             | 7  |

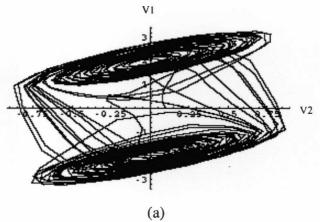

| 7.  | State Variables of Chaotic Signals Generated by Chua's Circuit (Mathematica Simulation): (a) $V_1$ vs. $V_2$ , (b) $V_1$ vs. $V_3$ , and (c) $V_2$ vs. $V_3$ | 8  |

| 8.  | Nonlinear Resistor Implemented With Two OTAs                                                                                                                 | 10 |

| 9.  | Transfer Characteristics:(a) OTA A Transfer Characteristic and (b)<br>OTA B Transfer Characteristic                                                          | 11 |

| 10. | OTA Architecture                                                                                                                                             | 12 |

| 11. | Gyrator Using Two OTAs and a Capacitor                                                                                                                       | 14 |

| 12. | Transfer Characteristic of OTAs:(a) $g_a = -1.0mA/V$ , (b)<br>$g_b = -0.5mA/V$ , (c) $g_c = -0.5mA/V$ and (d) $g_d = -2.0mA/V$ .                             | 18 |

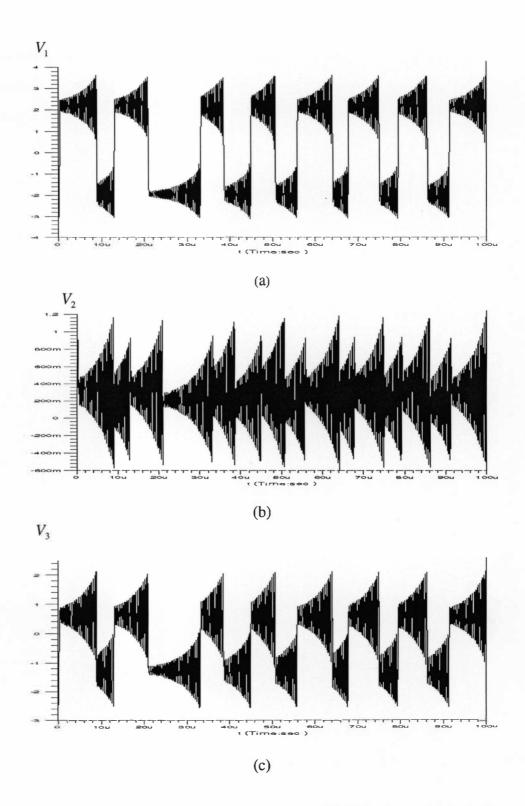

| 13. | Chaotic Signal Generated by Mentor Graphics: (a) $V_1$ , (b) $V_2$ and (c) $V_3$                                                                             | 20 |

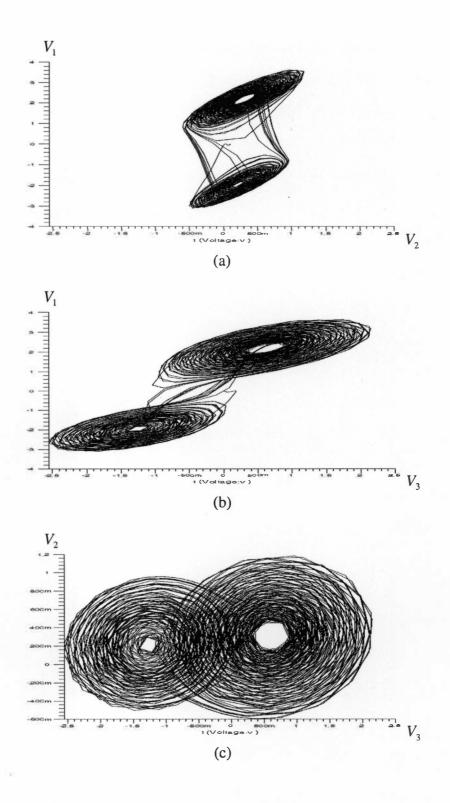

| 14. | State Variable of Chaotic Signals:(a) $V_1$ vs. $V_2$ , (b) $V_1$ vs. $V_3$ and (c) $V_2$ vs. $V_3$                                                          | 21 |

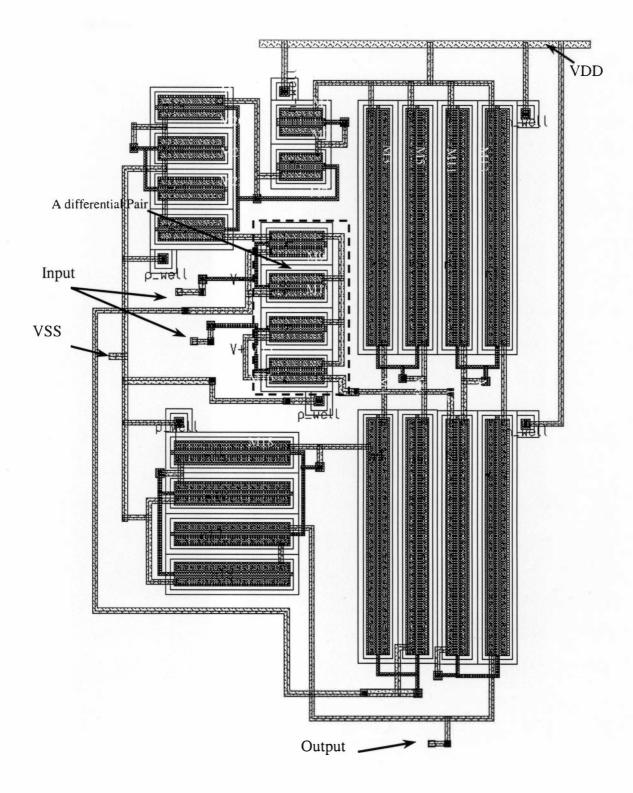

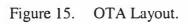

| 15. | OTA Layout                                                                                                                                                   | 23 |

| 16. | Layout of Chua's Circuit                                                                                                                                     | 25 |

# List of Figures—continued

| 17. | Simulations of Chua's Circuit After Back-Annotation:(a) $V_1$ , (b) $V_2$ and |    |

|-----|-------------------------------------------------------------------------------|----|

|     | (c) <i>V</i> <sub>3</sub>                                                     | 26 |

| 18. | Simulations of State Variable of Chua's Circuit After Back-                   |    |

|     | Annotation:(a) $V_1$ vs. $V_2$ , (b) $V_1$ vs. $V_3$ and (c) $V_2$ vs. $V_3$  | 27 |

| 19. | Disconnected Chua's Circuit Architecture                                      | 28 |

| 20. | Chip Configuration                                                            | 28 |

| 21. | Final Chip Layout                                                             | 30 |

#### CHAPTER I

## INTRODUCTION

In the past several years, synchronized chaos has been studied extensively. Applications include secure communication systems and associative memory [1]. This thesis describes an integrated circuit (IC) implementation of a popular chaotic oscillator based on previous work presented in [2-3].

## Associative Memory

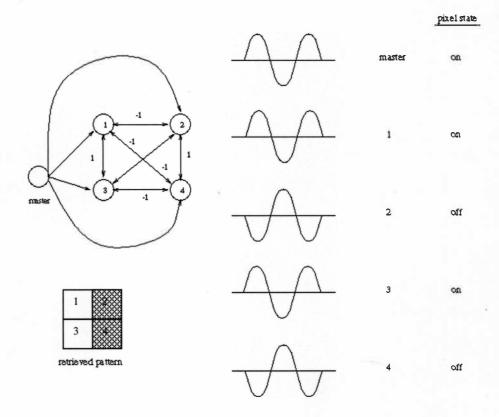

An associative memory (AM) stores memory patterns. The patterns are recalled via the presentation of a key pattern [1]. The associative memory is also able to perform noise reduction and pattern separation [4] as shown in Figure 1.

Figure 1. Two Cases of AM Recall Demonstrating Noise Reduction and Pattern Separation. A Diamond, Circle and Square are Stored Patterns (A. Lozowski et.al, 1996).

Source: A. Lozowski, et al. Chaotic CNN for Image Segmentation, in Proceedings of the 4<sup>th</sup> International Workshop on Cellular Neural Networks (CNNA'96), (Seville, Spain), June 24-26 1996: p.223 This figure shows two examples of associative memory operation. The recovery of an incomplete diamond shape demonstrates the noise reduction property of the AM. The associative memory selects the closest match to this key pattern, yielding a complete diamond shape for the output. For pattern separation, a combination of square and circle shapes is presented to the associative memory. The resulting output is a separation of these two patterns.

Interconnected nonlinear oscillators may be used to build an associative memory [4]. A simplified description is shown in Figure 2 [1].

Figure 2. Block Diagram of a Simple Associative Memory (D.A. Miller, et. al, 1999).

Source: D.A Miller, et al. Enhancing Electrical and Computer Engineering Education by Building Electronic Artificial Neural Networks. North Central Section Annual Meeting Proceedings. April 8-10, 1999: p. 180

2

Each circle represents an oscillator. The lines indicate the presence of a coupling element which tends to either force two oscillators to have either the exact same (synchronization) or the exact opposite (anti-synchronization) output signal. These two states may be used to store binary bit information [1, pp.178].

The synchronization refers to "1 or ON" and anti-synchronization refers to "0 or OFF" in binary bit. The arrows indicate the direction of this influence. In Figure 2, four bits are represented. The key pattern is coupled to the network via specification of the signs (- or +) of the connections to the master free running oscillator. This free running master oscillator provides a reference to which other oscillators (1-4) may be compared to indicate the value of the stored bit [1].

Chua's Circuit: An Easily Realized Chaotic Oscillator

## Description

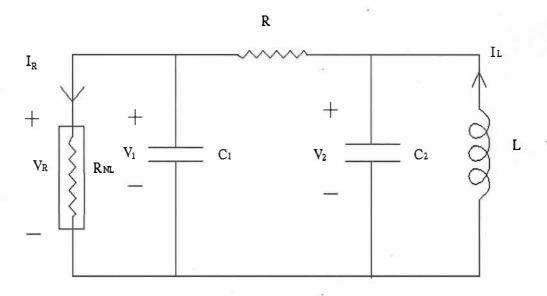

This section describes the chaotic oscillator chosen for implementation. Chua's circuit is the simplest electronic circuit that can produce chaotic signals. The circuit is very simple as shown in Figure 3. It contains three linear storage components, one active resistor and one non-linear resistor. Due to its simplicity, Chua's circuit is widely used to study chaotic behavior. Furthermore, this circuit has been proven to exhibit chaotic behavior [2-3,5-6]. Chua's circuit has been physically realized using both discrete and integrated circuits.

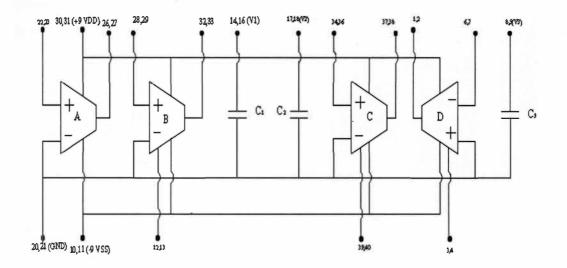

A typical discrete design [5-6] uses a combination of operational amplifiers. The design of interest uses CMOS technology [2-3]. In this study, the design will emulate Cruz's design approach [2-3]. The circuit design uses four operational transconductance amplifiers (OTAs). Three storage capacitors are built using doublepoly technology. The resistor will be connected externally. Major components inside the chip will be isolated from each other and connected externally as well. This enables testing each section separately and the opportunity to replace any internal parts which do not work properly.

Chua's circuit is described by the following set of differential equations:

$$\frac{dv_1}{dt} = \frac{1}{RC_1}(v_2 - v_1) - \frac{I_R}{C_1}$$

(1.1)

$$\frac{dv_2}{dt} = \frac{i_L}{C_2} - \frac{1}{RC_2}(v_2 - v_1)$$

(1.2)

$$\frac{di_L}{dt} = -\frac{v_2}{L}$$

(1.3)

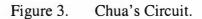

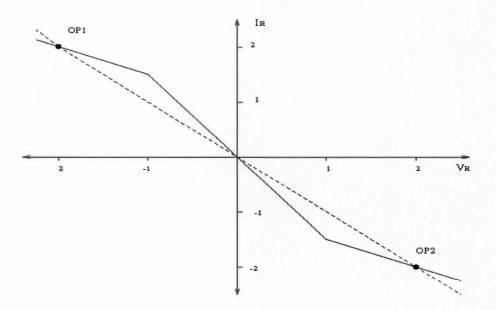

where  $v_1$  is voltage across capacitor  $C_1$ ,  $v_2$  is voltage across capacitor  $C_2$ ,  $i_L$  is the current through inductor L, and  $I_R$  is the current through non-linear resistor. The relationship of  $I_R$  and  $V_R$  is shown in Figure 4.

Figure 4. Driving-Point Characteristic of the Nonlinear Resistor.

This relationship can be expressed as:

$$I_{R} = f(v_{R}) = \begin{cases} G_{b}v_{R} + (G_{b} - G_{a}) & \text{if } v_{R} < -E \\ G_{a}v_{R} & \text{if } -E \le v_{R} \le E \\ G_{b}v_{R} + (G_{a} - G_{b}) & \text{if } v_{R} > E \end{cases}$$

(1.4)

where  $G_a$  is slope of  $I_R$  when  $-E \le v_R \le E$ ,  $G_b$  is slope of  $I_R$  when  $v_R < -E$  and  $v_R > E$ , and E is the break point.

## Simulation of Circuit Differential Equations

Chua's equation will be simulated by using Mathematica. The source code is shown in Appendix A.

Chua's circuit may be represented in a normalized form where:

$$\alpha = C_2 / C_1 \tag{1.5}$$

$$\beta = R^2 C_2 / L \tag{1.6}$$

$$G_a = -(1+\varepsilon)/R \tag{1.7}$$

$$G_h = -(1 - \varepsilon) / R \tag{1.8}$$

5

The following values of these parameters have been formed to provide robust chaotic behavior for use in associative memories [A.Lozowski]:  $\alpha = 10$ ,  $\beta = 16$  and  $\varepsilon = -0.5$ . Thus, we select  $R = 1000 \Omega$ ,  $C_1 = 15 pf$  and E = 1 V. Then  $C_2 = 150 pf$ , L = 9.375  $\mu$  H,  $G_a = -0.5$  mA/V and  $G_b = -1.5$  mA/V.

Before simulating the circuit, the DC operating point of the circuit has been calculated. This computation is illustrated in Figure 5.

Figure 5. Computation of DC Operating Point.

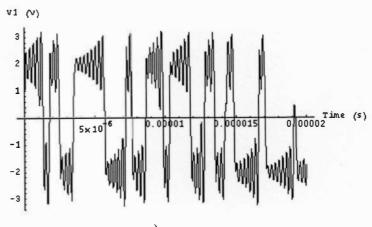

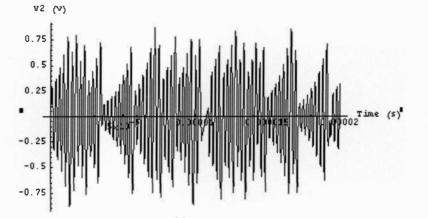

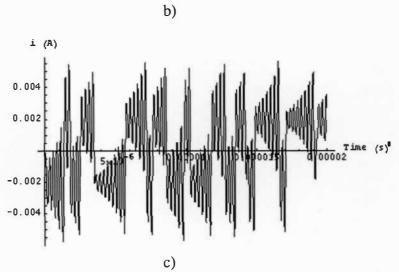

The operating points are (-2,2) and (2,-2). These points are unstable; however, the output of circuit still remains bounded [5-6]. The state is repelled from one point to another as indicated in Figure 6. Note the complex behavior of these signals. The system state, though completely deterministic, is unpredictable after a short time. Thus the system states appear to be random. This property is useful in endowing AMs with pattern separation abilities.

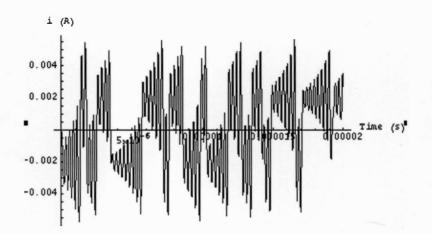

Figure 6. Chaotic Signal Generated by Chua's Circuit (Mathematica Simulation): (a)  $V_1$ , (b)  $V_2$ , and (c) *i*.

V1 0.004 -0.004 002 (b)

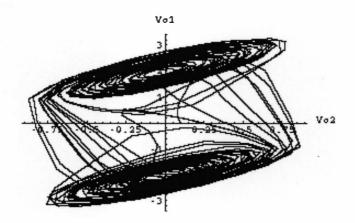

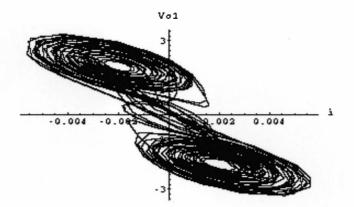

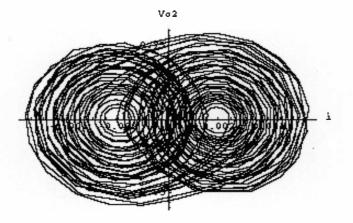

State Variables of Chaotic Signals Generated by Chua's Circuit (Mathematica Simulation):(a)  $V_1$  vs.  $V_2$ , (b)  $V_1$  vs.  $V_3$ , and (c)  $V_2$  vs.  $V_3$ . Figure 7.

The result is a chaotic signal which oscillates around the previously described fixed points. Example simulated waveforms are shown in Figures 6 and 7. Having described Chua's circuit and its applications, the design of an integrated circuit implementation will now be considered.

## CHAPTER II

## CIRCUIT DESIGN

## Nonlinear Resistor

In this chapter, an IC design of Chua's circuit is described. Again, note that this design is based in large part on the work in [2-3].

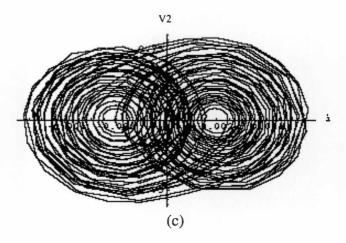

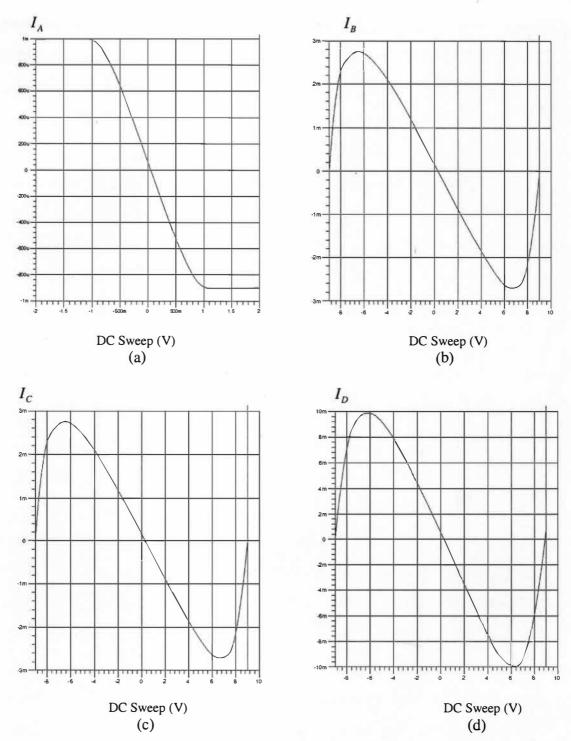

This design should realize the driving-point characteristic of Figure 4. The nonlinear resistor is implemented by two operational transconductance amplifiers (OTAs) connected in series [2-3] as shown in Figure 8.

Figure 8. Nonlinear Resistor Implemented With Two OTAs.

The  $I_R$  current is the sum of  $I_A$  and  $I_B$ , where  $I_A$  is OTA A's current and  $I_B$  is OTA B's current. The transfer characteristics of the two OTAs should be

$$I_{A} = f_{A}(v_{R}) = \begin{cases} -g_{A}E & if \quad v_{R} < -E \\ g_{A}v_{R} & if \quad -E \le v_{R} \le E \\ g_{A}E & if \quad v_{R} > E \end{cases}$$

(2.1)

$$I_{B} = f_{B}(v_{R}) = g_{B}V_{R}$$

(2.2)

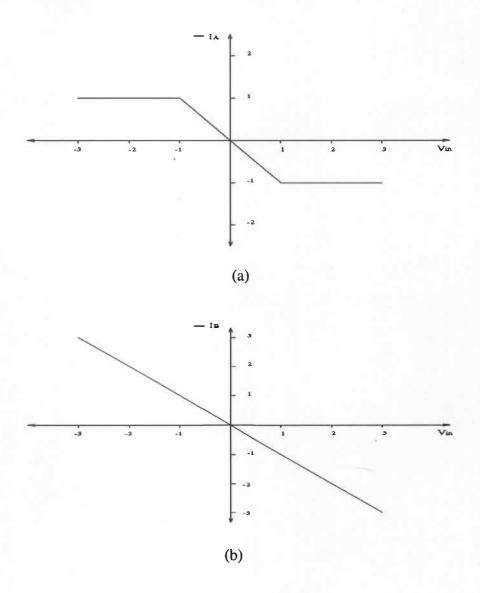

The transfer characteristics are shown in Figure 9.

Figure 9. Transfer Characteristics: (a) OTA A Transfer Characteristic, and (b) OTA B Transfer Characteristic.

The sum  $I_R$  is shown in Figure 4. Thus,

$$G_A = g_A + g_B \text{, and}$$

(2.3)

$$G_B = g_B.$$

(2.4)

## OTA Design

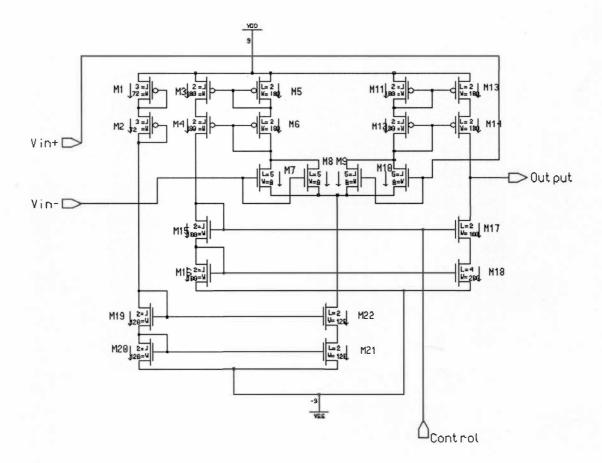

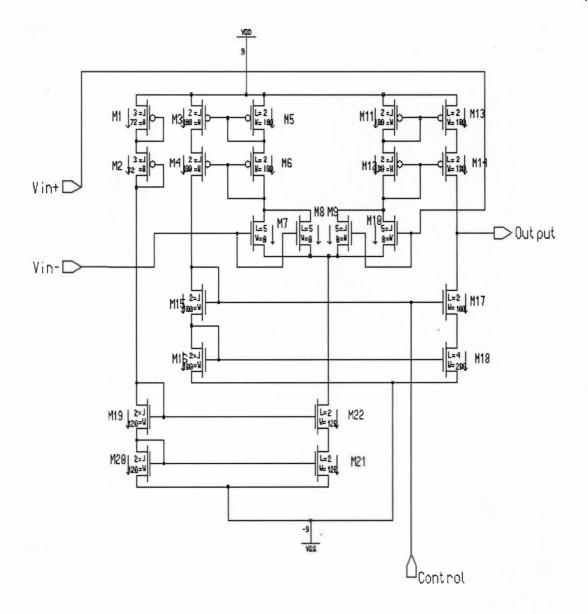

The OTA design is based on an input differential pair structure with relatively large transistors  $(M_7 - M_{10})$ . This can reduce flicker noise [2-3]. The OTA architecture is shown in Figure 10.

A reference current is generated by the cascading of  $M_1$ ,  $M_2$ ,  $M_{19}$  and  $M_{20}$ . This cascading increases the circuit output resistance. NMOS transistors  $M_7 - M_{10}$  form a differential pair. Use of a symmetric configuration with three current mirrors  $(M_3 - M_6 \text{ and } M_{11} - M_{22})$  will reduce the offset and increase the output swing [2-3].

In this research, Chua's circuit parameters have been fixed to obtain chaotic signals. From previous chapter, we selected  $R = 1000 \ \Omega$ ,  $G_a = -1.5 \ mA/V$ ,  $G_b = -0.5 \ mA/V$ ,  $C_2 / C_1 = 10$ ,  $L = R^2 C_2 / 16 \ R$  and E = 1V. Selecting  $C_2 = 150 \ pF$  yields  $C_1 = 15 \ pF$  and  $L = 0.00932 \ mH$ . From equations 2.4 and 2.5, the transfer characteristics of OTA A and OTA B will be  $g_a = -1.0 \ mA/V$  and  $g_b = -0.5 \ mA/V$ , respectively. The dimension of a differential pair of an OTA obtained by solving

$$g_a = \sqrt{\mu Cox \frac{W_A}{L_A}} I_A$$

and (2.4)

$$I_A = g_a E \,, \tag{2.5}$$

where  $I_A$  is reference current of the OTA A and  $\mu Cox$  is dependent upon the CMOS technology. The  $\mu Cox$  value used in the design is 52.58  $\mu A/V^2$  for NMOS transistors and 18.38  $\mu A/V^2$  for PMOS transistors. This yields  $W_A/L_A = 2 \times 33/3$ ,  $W_B/L_B = 2 \times 8/5$ ,  $I_A = 1.0$  mA and  $I_B = 3.6$  mA.

In additional, OTA B has extra terminals labeled "control". These terminals are connected to the gates of NMOS transistors ( $M_{15}$  and  $M_{17}$ ). The control will connect to an external resistor and a voltage source. This voltage source either increases or decreases the mirror current dependent on voltage source. If the current increases, the transfer characteristic becomes steeper. On the other hand, if the mirror current decreases, the transfer characteristic becomes less steep.

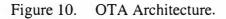

#### Gyrator

Due to the inability of CMOS technology to provide an inductor, an OTA based gyrator is used. This consists of two OTAs and a capacitor. The design is shown in Figure 11.

Figure 11. Gyrator Using Two OTAs and a Capacitor.

i

For OTA C, we can use the architecture of OTA B with a slope of -0.5 mA/V. For OTA D,  $g_D$  is selected at -2.0 mA/V. OTA D needs enough voltage swing for  $V_{C3}$  and sufficient current swing for  $I_D$ . The current  $I_D$  and current  $I_L$  are identical as shown in Figure 3. From the simulation of Chua's circuit by Mathematica, Figure 6(c) showed that the maximum current  $I_C$  is 6 mA. Thus, OTA D needs to generate enough current to cover this range. This can be done by increasing the dimension of active load. The voltage swing can be increased by increasing the dimension of transistors ( $M_3 - M_6$  and  $M_{11} - M_{14}$ ). The control of OTA C and D can be done as OTA B.

In Figure 11, The value of  $g_c, g_d$ , and  $C_3$  can be obtained from

$$i_c = g_c v_2 = C_3 \frac{dv_{c3}}{dt}$$

, and (2.7)

$$L = g_d v_{c3} \tag{2.8}$$

The Lapalce transform yields

$$I_{c}(s) = g_{c}V_{2}(s) = sCV_{c3}(s) \text{, and}$$

(2.9)

$$I_{L}(s) = g_{d}V_{c3}(s)$$

(2.10)

Rearranging the equations, we obtain the transfer function

$$\frac{I_L(s)}{V_2(s)} = \frac{g_c g_d}{sC_3}$$

(2.11)

which indicates that this circuit has an inductance of

$$L = \frac{C_3}{g_c g_d} \tag{2.12}$$

The design value for L is 9.375 mH. Selecting  $g_c = -0.5 \ mA/V$  and  $g_d = -2.0 \ mA/V$ , yields  $C_3 = 9.375 \ pf$ . The actual value in the final design of  $C_3$  is 13 pf. This will be discussed in the next chapter.

## CHAPTER III

## CIRCUIT SIMULATION, LAYOUT AND VERIFICATION

## Circuit Simulation

Spice3f4, developed by UC Berkley, and Mentor Graphics were used to design, simulate, and test the transfer characteristics of each OTA and verify the operation of Chua's circuit. The design process initially used Spice3f4 since this package is easier to use. MOSFET level 3 model parameters obtained from the MOSIS service fabrication are used. N91W test run as summarized in Table 1. The model level 3 parameters are shown in Appendix D.

### Table 1

| Parameters      | n-channel | p-channel | Units          |

|-----------------|-----------|-----------|----------------|

| V <sub>th</sub> | 0.809     | 0.846     | v              |

| μCox            | 52.58     | 18.38     | $\mu A/V^2$    |

| γ               | 0.41      | 0.55      | $\sqrt{V}^{*}$ |

## Technological Data

The Spice3f4 source code of the OTAs and Chua's circuit are shown in Appendix A as well. After sizing the transistors to yield the desired simulated results using Spice3f4 the design was further developed using Mentor Graphics since this package also provides layout tools (IC station). The design in Mentor Graphics used BSIM level 49 parameters obtained from the N91W fabrication test run by MOSIS service. The BSIM model parameters are shown in Appendix C. The simulation procedure started with entering the OTA designs into the Design Architecture in Mentor Graphics. The transistor dimensions of obtained from spice3f4 simulations were used for the initial design. To have the desired outputs in Mentor Graphics, the dimension of transistors needed to be changed because of the different simulation model (BSIM). The final transistor dimensions of the OTAs are shown in Table 2.

#### Table 2

| Mask | Device | Dimensions |

|------|--------|------------|

|------|--------|------------|

| Device                             |    | A<br>(microns) |     | B&C<br>(microns) |     | D<br>(microns) |  |

|------------------------------------|----|----------------|-----|------------------|-----|----------------|--|

|                                    | w  | L              | w   | L                | w   | L              |  |

| M1, M2                             | 26 | 4              | 72  | 3                | 180 | 2              |  |

| M3, M4, M5, M6, M11, M12, M13, M14 | 40 | 2              | 180 | 2                | 400 | 2              |  |

| M7, M8, M9, M10                    | 33 | 3              | 8   | 5                | 30  | 5              |  |

| M15, M16, M17, M18                 | 70 | 2              | 100 | 2                | 200 | 2              |  |

| M19, M20, M21, M22                 | 40 | 2              | 120 | 2                | 200 | 2              |  |

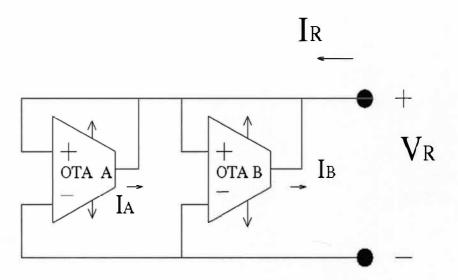

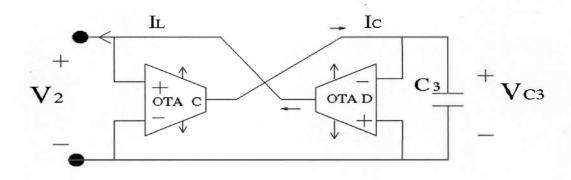

All designs were subsequently simulated using Accusim II in Mentor Graphics. Each OTA was simulated separately. Then all OTAs were combined with the required resistor and capacitors to form Chua's circuit. The OTA simulation results are shown in Figure 12.

Figure 12. Transfer Characteristic of OTAs:(a)  $g_a = -1.0mA/V$ , (b)  $g_b = -0.5mA/V$  (c)  $g_c = -0.5mA/V$ , and (d)  $g_d = -2.0mA/V$ .

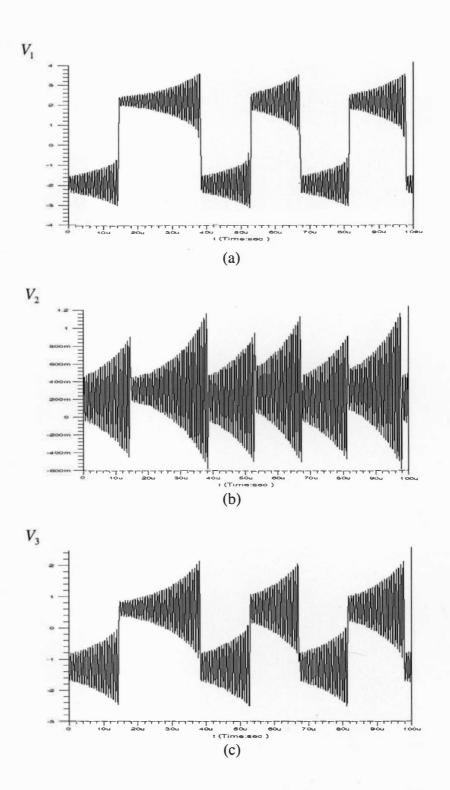

Note that the transfer characteristics are offset; nevertheless; these characteristics yielded acceptable behavior. The transistors dimension can be adjust to yield 1.0 mA for  $I_A$  but we cannot obtain  $I_B = 3.6$  mA with  $g_b = -0.5 m A/V$ . If we increase the dimension of  $M_1$  and  $M_2$ , the slope  $g_b$  will less than -0.5 m A/V. The maximum current we can obtain from OTA B was 2.8 mA and the range of voltages before the second break point is -6.2 V and 6.1V. However, this current and range of voltage are sufficient for the swing of  $V_1$ . For OTA D, the design needs a wide voltage range to yield the maximum linear region. As a result, the dimension of the current mirror and active load is very large (400/2 microns for  $M_3 - M_6$  and  $M_{11} - M_{14}$  transistor and 180/2 for active load). After observing all desired outputs of the OTAs, these OTA designs were used to build Chua's circuit in the Design Architecture. This circuit used  $R = 1000 \Omega$ ,  $C_1 = 15 pf$ ,  $C_2 = 150 pf$ , and  $C_3 = 16 pf$ . The value of  $C_3$  yielded improved characteristics as compared to the previously computed value of 9.375 pf. The capacitors were used a 2  $\mu m$  double-POLY CMOS technology by implementing POLY1 and POLY2 layers (called Electrode in Mentor Graphics) as capacitor plates. The value of capacitor obtains from

$$C = AC' \tag{3.1}$$

where A is an area ( $\mu m^2$ ) and C' is capacitance per unit area. This design used C' = 462 pF / mm<sup>2</sup> (see N91W test run in appendix D). That made the POLY area for  $C_1 = 32.47 mm^2$ ,  $C_2 = 324.7 mm^2$  and  $C_3 = 34.63 mm^2$ . In simulation, the initial voltages of capacitors have been set to small values ( $V_{C1}(0) = 0$  V,  $V_{C2}(0) = 0.1$ V,  $V_{C3}(0) = 0$ V). The result chaotic signals of  $V_1$ ,  $V_2$  and  $V_3$  are shown in Figure 13.

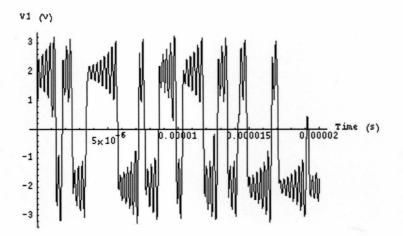

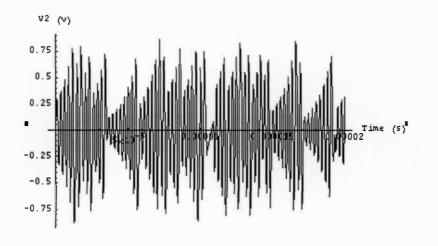

Figure 13. Chaotic Signals Generated by Mentor Graphics:(a)  $V_1$ , (b)  $V_2$ , and (c)  $V_3$ .

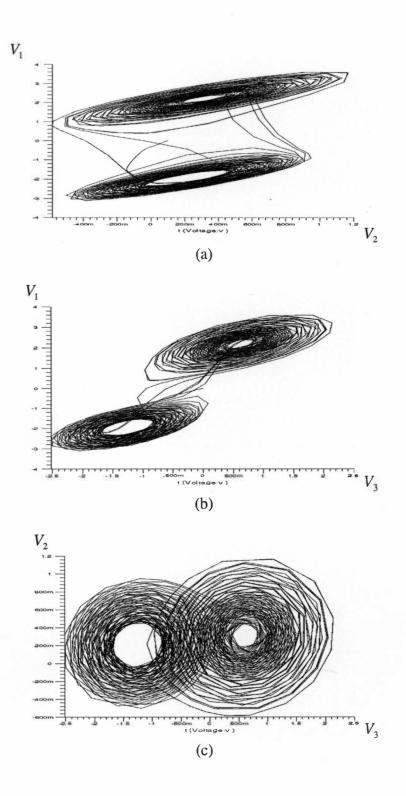

Figure 14. State Variable of Chaotic Signals:(a)  $V_1$  vs.  $V_2$ , (b)  $V_1$  vs.  $V_3$ , and (c)  $V_2$  vs.  $V_3$ .

From Figure 13 (a), the chaotic signal oscillated around the +2v and -2v fixed point corresponding to the chaotic signal plotted by solving Chua's equation numerically. Further verification of the chaotic nature of these signals other than this qualitative comparison requires tools beyond the scope of this thesis. The next step of the CMOS chaotic oscillator design is layout and parasitic extraction using IC station.

## Layout and Parasitic Extraction

The layout and parasitic extraction process includes the process of Design Rule Checking (DRC) and a Layout versus Schematic check (LVS). The DRC is a dimensional check of layout to verify that no design rules were violated. The LVS is the process that checks to see what was drawn in the layout has the same electrical functionality as the schematic. The LVS will show errors or missing connections if layout devices did not match with schematic devices. An example of LVS report is shown in Appendix C. To avoid mistakes and make the layout easy to fix when performing DRC and LVS, the design is best laid out separately. This means that each OTA will be laid out and tested against Design Rule Checking (DRC) and Layout versus Schematic (LVS) individually before forming Chua's circuit. Our layout does not address issues of device mismatches through variations in the die or temperature. This will be subject of later work. The layout of OTA is shown in Figure 15.

After all OTAs passed DRC and LVS checks successfully, the layout needed to be analyzed for parasitic extraction (IC trace) in the final step. The parasitic resistance and capacitance was back-annotated and the circuit was re-simulated. The performance of the circuit is satisfactory with back-annotation, thus the design is complete. Next, each OTA layout was merged into the Chua's circuit layout. This circuit needs to pass DRC and LVS as well. IC station does not currently have

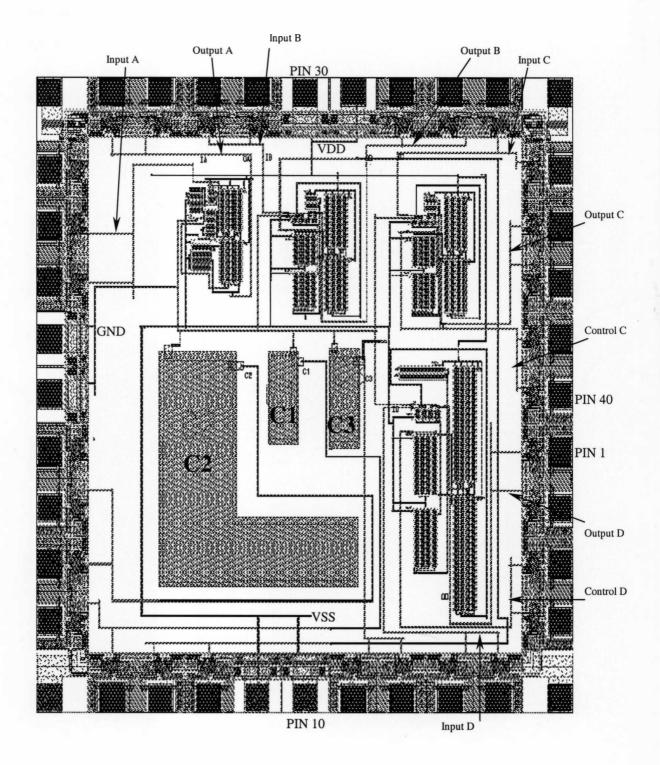

automated capacitor or resistor placement. It has only NMOS and PMOS transistor placement. Thus, the designer had to place capacitors manually. The resistor is an external device. The capacitors used were a 2  $\mu m$  double-poly CMOS technology as referred to in a previous section. Chua's circuit was performed DRC and LVS check. There were no errors in DRC check and passed LVS check. Then, the back-annotation information was generated. The layout of Chua's circuit is shown in Figure 16.

## Verification

After the parasitic were extracted, the simulation of the post-layout circuit needed to be done with the back-annotated information. Simulation required that resistor be added as an external device. The results are shown in Figures 17 and 18.

It can be seen that the chaotic signal resulting from post back-annotation simulation takes a slightly more time for swinging from one fixed point (-2V) to the other fixed point (+2V). However, the back-annotation circuit still generates a qualitatively acceptable chaotic signal. Verification of the chaotic nature of the signal will be the subject of later work.

### Chip Architecture

The Chua's circuit design uses isolated OTAs and capacitors. These will be connected outside the chip. The circuit also requires an external resistor. OTA B, C and D have extra pins labeled control. These pins are used for adjusting the value of transfer function of OTA. The Chua's circuit architecture is shown in Figure 19.

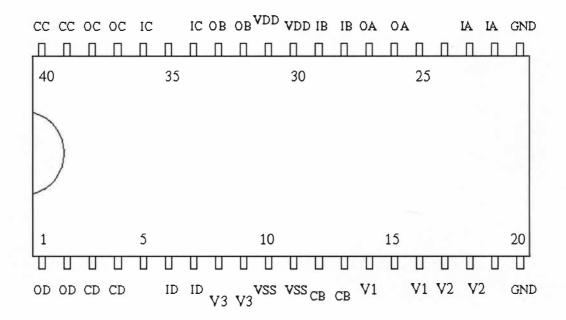

The circuit uses a DIP 40 pin chip. The inputs and outputs of Chua's circuit had been assigned to the chip as shown in Figure 20.

Figure 16. Layout of Chua's Circuit.

Figure 17. Simulations for Chua's Circuit After Back-Annotation: (a)  $V_1$ , (b)  $V_2$ , and (c)  $V_3$ .

Figure 18. Simulations for State Varible of Chua's Circuit After Back-Annotation: (a)  $V_1$  vs.  $V_2$ , (b)  $V_1$  vs.  $V_3$ , and (c)  $V_2$  vs.  $V_3$ .

Figure 19. Disconnected Chua's Circuit Architecture.

Figure 20. Chip Configuration.

The final chip design needs to have a pad-frame. The MOSIS Design Kit (MDK) provides an analog DIP 40 pad-frame. This pad-frame contains 40 pins. The disconnected Chua's circuit was wired to pad-frames and pin numbers were assigned. The DRC was performed again to make sure that no error while wring. At this time, the DRC found 4186 errors. The layout was re-checked and was found that the providing padframe form MDK had 4054 errors and each analog pad had 33 errors. The DRC error report is shown in Appendix C. One must assume that the libraries are correct that the pads are taking advantage of specialized design. A DRC was performed again and a DRC check of the core circuit returned a result of zero error. The LVS check is not helpful since this final chip has disconnected circuitry. Next, the final layout of Chua's chip was converted to MOSIS formats which are either GDSII or CIF formats. Thus, the chip is ready to be fabricated by the MOSIS service. The final chip layout is shown in Figure 21.

Figure 21. Final Chip Layout.

#### CHAPTER IV

### CONCLUSION AND FUTURE WORK

This thesis described the design and test of a CMOS chaotic oscillator design (Chua's circuit) based on previous work by Cruz (1993) using Spice3f4 and Mentor Graphics. The circuit layout was performed using Mentor Graphics. The chip architecture used isolates OTAs and capacitors for ease of testing. The circuit will also use an external resistor. The simulation result of this circuit produced chaotic signals which are in close qualitative agreement with numerical predictions based on the Chua's equation. Files necessary for fabrication were generated.

The layout did not address the issues of device mismatches and thermal effects. The operation of the vendor supplied input/output pads needs to be verified. These topic will be the subjects of later work. The chaotic nature of the signals also requires future verification. Nevertheless, fabrication of this IC will provide the foundation for future work using this oscillator.

#### REFERENCES

- [1] Miller, D.A., Severance, F.L, Barr, J., Barr, L., Chansilp, B., Kowalski, K.L., Lange, C.E., Marikar, A., Tolliver, J.K., Vieth, J.W. and Whitney, J.M., Enhancing Electrical and Computer Engineering Education by Building Electronic Artificial Neural Networks. North Central Section Annual Meeting Proceedings. April 8-10, 1999: 176-184.

- [2] Cruz, J.M. and Chua L.O., A CMOS IC Nonlinear Resistor for Chua's Circuit. IEEE Transactions on Circuits and Systems Dec 1992: 985-995.

- [3] Cruz, J.M. and Chua L.O., An IC Chip of Chua's Circuit. IEEE Transaction on Circuits and Systems. Oct 1993: 614-625.

- [4] Lozowski, A, Cholewo, T.J, Jankowski, S. and Tworek, M., Chaotic CNN for Image Segmentation. In Proceedings of the 4<sup>th</sup> International Workshop on Cellular Neural Networks (CNNA'96), Seville, Spain. June 24-26, 1996. pp. 219-223.

- [5] Kenedy, M.P., "Three Steps to Chaos-Part I: Evolution." IEEE Transactions on Circuits and Systems Oct. 1993: 640-656.

- [6] Kenedy, M.P., "Three Steps to Chaos-Part II: A Chua's Circuit Primer." IEEE Transactions on Circuits and Systems Oct. 1993: 657-674.

Appendix A

# Mathematica Code

#### Listing of Mathematica's script for running Chua's equation.

E1=1;c1=15\*10^-12;c2=150\*10^-12;L=9.375\*10^-6;G=0.001;m1=-0.5\*10^

-3;m2=-1.5\*10^-3;(

$sol=NDSolve[\{v1'[t]==(G/c1)(v2[t]-v1[t])-((1/c1)(m1 v1[t]+0.5(m2-m1)(Abs[v1[t]+E1]-Abs[v1[t]-E1]))),v2'[t]==(G/c2)(v1[t]-v2[t])+(i[t]/c2),i'[t]==-(v2[t])+(i[t]/c2),i'[t]==-(v2[t]/L),v1[0]==0,v2[0]==0.1,i[0]==0\},\{v1,v2,i\},\{t,0,0.0001\},MaxSteps>100000]$

{ $\{v \rightarrow InterpolatingFunction[\{\{0.,0.0001\}\}, <>\}, v2 \rightarrow InterpolatingFunction[\{\{0.,0.0001\}\}, <>], i \rightarrow InterpolatingFunction[\{\{0.,0.0001\}\}, <>]}}$

$v1=Plot[Evaluate[v1[t] /. sol], \{t, 0, 0.00002\}];$

Show[v1,AxesLabel->{"Time (s)", "v1 (V)"}]

-Graphics-

V2=Plot[Evaluate[v2[t] /. sol],{t,0,0.00002}]; Show[v2,AxesLabel->{"Time (s)", "v2 (V)"}]

-Graphics-

i=Plot[Evaluate[i[t] /. sol],{t,0,0.00002}];

Show[i,AxesLabel->{"Time (s)", "i (A)"}]

-Graphics-

v1v2=ParametricPlot[{Evaluate[v2[t] /. sol][[1]],Evaluate[v1[t] /. sol][[1]]},{t,0,0.00002}];

plot1=Show[v1v2,AxesLabel->{"Vc2", "Vc1"}]

-Graphics-

v1i=ParametricPlot[{Evaluate[i[t] /. sol][[1]],Evaluate[v1[t] /. sol][[1]]},{t,0,0.00002}]

plot2=Show[v1i,AxesLabel->{"i", "Vc1"}]

-Graphics-

v2i=ParametricPlot[{Evaluate[i[t] /. sol][[1]],Evaluate[v2[t] /. sol][[1]]},{t,0,0.00002}]

plot3=Show[v2i,AxesLabel->{"i", "Vc2"}]

36

-Graphics-

Appendix B

Spice Model

#### Source code for simulating the circuit using Spice3f4.

This file is Chua's circuit file which contains three subfiles, botaa.mod, botab.mod and botad.mod.

\*chua

```

*.OPTIONS NODE NOPAGE

** power Supply

.include botaa.mod

.include botab.mod

.include botad.mod

xamp1 1 2 3 4 5 botaa

xamp2 1 2 3 4 6 botab

xamp3 10 2 3 4 11 botab

xamp4 2 12 3 4 13 17 botad

VCC 3 0 DC 9v

VSS 4 0 DC -9v

*VP 1 0 dc 0v

VN 2 0 dc 0v

va 1 5 dc 0v

vb 1 6 dc 0v

vd 10 13 dc 0v

vc 12 11 dc 0v

R 1 10 1000

c3 12 2 10pf

c1 1 2 15pf

c2 10 2 150pf

*L 10 2 .009375mH

IC v(1) = 0v v(10) = 0v

IC v(12) = 0v

.tran .01us .02ms

*.DC VP -8 8 0.1

.plot TRAN i(L) v(10) v(1) v(12) i(vc) i(vd)

*.plot DC v(100) i(va) i(vb) i(vc) i(vd) i(vr)

*.op

. PROBE

. END

```

This file is OTA A subfile which contains transistors and transistor model simulation.

\*otaa.mod

\*.OPTIONS NODE NOPAGE

\*\* power Supply .subckt botaa 100 2 1 4 5 \*VCC 1 0 DC 5v \*VNEG 4 0 DC -5V \*VP 100 0 DC 0v 0 DC 0v \*VN 2 100 5 DC 0v \*va \*vb 999 13 DC Ov \*vc DC Ov 99 5 M1 11 11 1 pfet W = 65UL = 10U1 1 pfet W = 65UM2 12 12 11 L = 10UM3 19 6 1 pfet W = 280 UL = 4U1 L = 4UL = 4UM4 13 7 19 1 pfet W = 280 UM5 6 6 1 1 pfet W = 280 U7 1 pfet W = 280U L = 4UM6 7 6 Μ7 7 2 10 4 nfet W = 66UL = 6U7 L = 6U M8 2 10 4 nfet W = 66UM9 9 100 10 4 nfet W = 66U L = 6U M10 9 100 10 4 nfet W = 66UL = 6U1 pfet W = 280U L = 4UM11 9 9 8 M12 8 8 1 1 pfet W = 280U L = 4UM13 8 14 1 1 pfet W = 280U L = 4UM14 9 5 14 1 pfet W = 280U L = 4U13 M15 13 16 4 nfet W = 140U L = 4U 16 M16 16 4 4 nfet W = 140U L = 4U13 M17 5 15 4 nfet W = 138U L = 4U M18 15 16 4 4 nfet W = 138U L = 4U M19 12 12 17 4 nfet W = 100U L = 5U M20 17 17 4 4 nfet W = 100U L = 5UM21 30 17 4 4 nfet W = 100U L = 5U M22 10 12 30 4 nfet W = 100U L = 5U

#### \*N91W SPICE LEVEL3 PARAMETERS

.MODEL nfet NMOS LEVEL=3 PHI=0.700000 TOX=4.0600E-08 XJ=0.200000U TPG=1

+ VTO=0.8093 DELTA=1.6500E+00 LD=4.1440E-07 KP=5.2580E-05

+ UO=618.2 THETA=5.3110E-02 RSH=1.5840E+01 GAMMA=0.4121

+ NSUB=3.7010E+15 NFS=5.9090E+11 VMAX=1.6760E+05

+ ETA=6.4270E-02

```

+ KAPPA=4.5740E-01 CGDO=5.2869E-10 CGSO=5.2869E-10

```

+ CGBO=3.4581E-10 CJ=1.4229E-04 MJ=6.2160E-01

```

+ CJSW=5.0307E-10

```

+ MJSW=2.4938E-01 PB=3.8328E-01

\* Weff = Wdrawn - Delta\_W

```

* The suggested Delta_W is 2.0000E-09

```

.MODEL pfet PMOS LEVEL=3 PHI=0.700000 TOX=4.0600E-08 XJ=0.200000U TPG=-1

+ VTO=-0.8460 DELTA=4.6140E-01 LD=4.9340E-07 KP=1.8388E-05

+ UO=216.2 THETA=1.0720E-01 RSH=5.1170E+01 GAMMA=0.5557 + NSUB=6.7290E+15 NFS=5.9090E+11 VMAX=2.6220E+05 ETA=7.9790E-02

+ KAPPA=1.0000E+01 CGD0=6.2948E-10 CGS0=6.2948E-10

+ CGBO=3.8539E-10 CJ=3.1476E-04 MJ=5.7042E-01 CJSW=3.1623E-10

+ MJSW=2.4970E-01 PB=8.8539E-01

\* Weff = Wdrawn - Delta\_W

\* The suggested Delta\_W is 1.6070E-07

\*.DC VP -2 2 0.1 \*.plot DC v(100) i(va) i(vb) i(vc) i(vd) \*.plot DC i(v1) i(va) i(vb) i(vc) i(vd) i(ve) i(vf) i(vg) \*.op \* . PROBE . ENDS This file is OTA B subfile which contains transistors and transistor model simulation. \*OTA` B ckt .subckt botab 100 2 1 4 5 \*VP 100 0 DC 0v \*VN 2 0 DC 0v \*va 100 5 DC 0v 999 13 DC Ov \*vb \*vc 99 5 DC Ov 11 1 pfet W = 230U L = 10UM1 11 1 12 12 M2 11 1 pfet W = 230U L = 10U 19 M3 6 1 1 pfet W = 350U L = 4U13 19 M4 7 1 pfet W = 350U L = 4UM5 1 pfet W = 350 L = 4 U6 6 1 7 7 M6 6 1 pfet W = 350 L = 4 U7 M7 2 10  $4 \text{ nfet } W = 15U \quad L = 10U$ M8 7 10 4 nfet W = 15U L = 10U 2 9 M9 100 10 4 nfet W = 15U L = 10U 9 M10 100 10 4 nfet W = 15U L = 10U M11 9 9 1 pfet W = 350 L = 4 U8 8 M12 8 1 1 pfet W = 350 L = 4 UM13 14 8 1 1 pfet W = 350U L = 4UM14 5 9 14 1 pfet W = 350U L = 4U 13 M15 13 16 4 nfet W = 200U L = 4U M16 16 16 4 4 nfet W = 200U L = 4U15 M17 5 13 4 nfet W = 200U L = 4U15 M18 16 4 4 nfet W = 200U L = 4UM19 12 12 17 4 nfet W = 600U L = 5U M20 17 17 4 4 nfet W = 600U L = 5U 30 17 M21 4 4 nfet W = 600U L = 5U 12 30 M22 10 4 nfet W = 600U L = 5U

#### \*N91W SPICE LEVEL3 PARAMETERS

.MODEL nfet NMOS LEVEL=3 PHI=0.700000 TOX=4.0600E-08 XJ=0.200000U TPG=1

- + VTO=0.8093 DELTA=1.6500E+00 LD=4.1440E-07 KP=5.2580E-05

- + UO=618.2 THETA=5.3110E-02 RSH=1.5840E+01 GAMMA=0.4121

- + NSUB=3.7010E+15 NFS=5.9090E+11 VMAX=1.6760E+05 ETA=6.4270E-02

- + KAPPA=4.5740E-01 CGDO=5.2869E-10 CGSO=5.2869E-10

- + CGBO=3.4581E-10 CJ=1.4229E-04 MJ=6.2160E-01 CJSW=5.0307E-10

- + MJSW=2.4938E-01 PB=3.8328E-01

- \* Weff = Wdrawn Delta\_W

- \* The suggested Delta\_W is 2.0000E-09

.MODEL pfet PMOS LEVEL=3 PHI=0.700000 TOX=4.0600E-08 XJ=0.200000U TPG=-1

```

+ VTO=-0.8460 DELTA=4.6140E-01 LD=4.9340E-07 KP=1.8388E-05

+ UO=216.2 THETA=1.0720E-01 RSH=5.1170E+01 GAMMA=0.5557

+ NSUB=6.7290E+15 NFS=5.9090E+11 VMAX=2.6220E+05 ETA=7.9790E-02

+ KAPPA=1.0000E+01 CGDO=6.2948E-10 CGSO=6.2948E-10

+ CGBO=3.8539E-10 CJ=3.1476E-04 MJ=5.7042E-01 CJSW=3.1623E-10

+ MJSW=2.4970E-01 PB=8.8539E-01

* Weff = Wdrawn - Delta_W

* The suggested Delta W is 1.6070E-07

*.DC VP -2 2 0.1

*.plot DC v(100) i(va) i(vb) i(vc) i(vd)

*.plot DC i(v1) i(va) i(vb) i(vc) i(vd) i(ve) i(vf) i(vg)

*.00

*.PROBE

. ENDS

This file is OTA D subfile which contains transistors and transistor

model simulation.

*OTA D ckt

*.OPTIONS NODE NOPAGE

** power Supply

.subckt botad 100 2 1 4 5 17

100 0 DC 0v

*VP

*VN

0 DC 0v

2

*va

100 5 DC 0v

*vb

999 13 DC 0v

99

*vc

DC Ov

5

*vbs 9999 17 DC 0v

M1

11

11

1 \text{ pfet } W = 400U \text{ L} = 4U

1

M2

12

12

11 1 pfet W = 400U L = 4U

1 pfet W = 800U L = 2U

M3

19

6

1

7

м4

13

19

1 \text{ pfet } W = 800U \text{ L} = 2U

M5

6

6

1 \text{ pfet } W = 800U \text{ L} = 2U

1

M6

7

7

1 \text{ pfet } W = 800 \text{ L} = 2 \text{ U}

6

7

L = 5U

M7

2

10

4 \text{ nfet } W = 40U

7

M8

2

10

4 nfet W = 40U

L = 5U

M9

9

100

10 4 nfet W = 40U

L = 5U

9

M10

100

10 4 nfet W = 40U

L = 5U

9

9

1 \text{ pfet } W = 800U \text{ L} = 2U

M11

8

8

1 \text{ pfet } W = 800U \text{ L} = 2U

8

M12

1

1 \text{ pfet } W = 800U \text{ L} = 2U

M13

14

8

1

1 \text{ pfet } W = 800 \text{U}

L = 2U

M14

5

9

14

13

13

16

4 \text{ nfet } W = 400U

L = 2U

M15

4 \text{ nfet } W = 400U \text{ L} = 2U

M16

16

16

4

13

15

4 \text{ nfet } W = 400U

M17

5

L = 2U

4 \text{ nfet } W = 400U

L = 2U

M18

15

16

4

M19

12

12

17

4 \text{ nfet } W = 400U

L = 4U

M2.0

17

17

4

4 \text{ nfet } W = 400U

L = 4U

M21

30

17

4

4 \text{ nfet } W = 400U \text{ L} = 4U

12

30

M22

10

4 \text{ nfet } W = 400U

L = 4U

```

\*N91W SPICE LEVEL3 PARAMETERS

.MODEL nfet NMOS LEVEL=3 PHI=0.700000 TOX=4.0600E-08 XJ=0.200000U TPG=1 + VTO=0.8093 DELTA=1.6500E+00 LD=4.1440E-07 KP=5.2580E-05 + UO=618.2 THETA=5.3110E-02 RSH=1.5840E+01 GAMMA=0.4121 + NSUB=3.7010E+15 NFS=5.9090E+11 VMAX=1.6760E+05 ETA=6.4270E-02 + KAPPA=4.5740E-01 CGDO=5.2869E-10 CGSO=5.2869E-10 + CGBO=3.4581E-10 CJ=1.4229E-04 MJ=6.2160E-01 CJSW=5.0307E-10 + MJSW=2.4938E-01 PB=3.8328E-01 \* Weff = Wdrawn - Delta\_W \* The suggested Delta\_W is 2.0000E-09 .MODEL pfet PMOS LEVEL=3 PHI=0.700000 TOX=4.0600E-08 XJ=0.200000U TPG=-1 + VTO=-0.8460 DELTA=4.6140E-01 LD=4.9340E-07 KP=1.8388E-05 + UO=216.2 THETA=1.0720E-01 RSH=5.1170E+01 GAMMA=0.5557 + NSUB=6.7290E+15 NFS=5.9090E+11 VMAX=2.6220E+05 ETA=7.9790E-02 + KAPPA=1.0000E+01 CGDO=6.2948E-10 CGSO=6.2948E-10 + CGBO=3.8539E-10 CJ=3.1476E-04 MJ=5.7042E-01 CJSW=3.1623E-10 + MJSW=2.4970E-01 PB=8.8539E-01 \* Weff = Wdrawn - Delta\_W \* The suggested Delta\_W is 1.6070E-07 \*.tran .01us 1ms \*.DC VP -2 2 0.1 \*.plot TRAN v(100) i(va) i(vb) i(vc) i(vd) v(5) \*.plot DC i(v1) i(va) i(vb) i(vc) i(vd) i(ve) i(vf) i(vg) \*.op \*.PROBE .ENDS

However, you can run each OTAs individually but you need to change from .mod file to .cir file and modify some Spice commands.

43

Appendix C

How to Use Mentor Graphics

#### Setup for running Design Architecture and AccuSim II

Source: David M. Zar http://germanium.ee.wustl.edu/dzar/tutorials/sdl/sdl\_toc.html

To run the Design Architecture and Accusim II, this script need to be put in MGC\_LOCATION\_MAP. You need to copy this file and put it in your working directory. This file below is an example of my Location\_Map file. You may ask for UNIX administrator for help.

MGC\_LOCATION\_MAP\_2

#

# MGC HEP Standard customization location

#

\$MGC\_HEP

/home3/software/mentorgr/mgc\_libs/gen\_lib/mgc\_hep

\$UNIVSIG /home3/software/mentorgr/mgc\_libs/gen\_lib/mgc\_hep

\$UNIVSIG\_LIB

/home3/software/mentorgr/mgc\_libs/gen\_lib/mgc\_hep

\$SCMOS\_IC\_TECH /home7/stpa098/s8chansi/mgc/scna20orbit.params3

#

# FROM ~mentorgr/mgc/etc/mgc\_location\_map

#

# MGC accuparts\_lib V8.5\_1

\$MGC\_APLIB

/home3/software/mentorgr/mgc\_libs/accuparts\_lib

# MGC asim\_templt\_lib V8.5\_1

\$MGC\_TEMPLATELIB

/home3/software/mentorgr/mgc\_libs/asim\_templt\_lib

# MGC accusim\_smb\_lib V8.5\_1

\$MGC\_SMBLIB

/home3/software/mentorgr/mgc\_libs/accusim\_smb\_lib

# BPL V8.5\_2.1 \$BPL\_RLS\_LIB /home3/software/mentorgr/bpl\_rls\_lib # MGC gen\_lib V8.4

\$MGC\_GENLIB

/home3/software/mentorgr/mgc\_libs/gen\_lib

# MGC misc\_lib V8.4

\$MGC\_MISCLIB

/home3/software/mentorgr/mgc\_libs/misc\_lib

# MGC passive\_lib V8.4\_2.1

\$MGC\_PASSIVELIB

/home3/software/mentorgr/mgc\_libs/passive\_lib

#### Setup for running IC station

This script will help you to run IC Station properly. You can put this file to your directory. The file below is an example for my directory. Ask for help from the UNIX administrator.

\$setup\_auto\_checkpoint(@on, 15);

\$setup\_new\_windows(@on, 0.5, 0.5, 1, 10, 0, 0, 5); \$setup\_reports([@shape, @path, @text, @property\_text, @instance, @device, @array, @row, @pin, @via\_object, @overflow, @net, @port], [@edges, @properties, @ports, @nets, @row], @window, @notranscript, ""); \$load\_process("\$MGC\_HEP/technology/ic/scmos"); \$load\_rules("\$MGC\_HEP/technology/ic/scmos.rules");

#\$add\_menu\_item(,\$menu\_bar\_item("MD\_K",

"mdk\_pulldown",,,"Red"),"user\_ic@@default\_menu\_bar");

\$load\_userware("/home7/stpa098/s8chansi/mgc/ic/mos", "user\_ic", @ample); \$load\_userware("/home7/stpa098/s8chansi/mgc/ic/mosfilter.ample","user\_ic", @ample);

\$load\_userware("\$stpa098/s8chansi/mgc/ic/ic\_area.ample", "user\_ic", @ample);

#### Using DA to Capture a Design

- 1. Invoke Design Architecture by typing **DA** & in your workstation.

- 2. Once DA is running, open new sheet by using either menu bar or palette menu. Put file name, then an empty sheet will pop up.

- 3. Now start drawing circuit. Use the Librarian icon to show the MDK palette menu.

- 4. Click on SDL to show the SDL parts palette menu.

- 5. Now place instances of the n-fet-3 and p-fet-3 (three terminal n-fet and p-fet) to form an OTA design shown in figure 1. To make easier, we'll go through the process (DA to post simulation) with an OTA. After passing every step, then we can capture, simulate, layout, and back-annotate Chua's circuit.

Figure 1. OTA Schematic.

- 6. Place VDD, VSS, port in, port out and GND from SDL palette menu. Then, wire up the components as shown in figure 1.

- 7. Before we can change any value and port name, you need to select properties. Do this by clicking on *Set Select Filter*, then the *Setup Select Filter* box will show up. Click on *Properties* and leave others at defaults. Accept the box (Figure 2).

| Setup            | Select Filter            |

|------------------|--------------------------|

| Add/Route        | Text Draw                |

| Selection Filter | will allow selection of: |

| Comments         | Properties               |

| Frames           | Segments                 |

| 🔎 Instances      | Symbol Pins              |

| Nets             | Comment Text             |

| Fins             | Vertices                 |

Figure 2. Setup Select Filter Box.

Now you can change value and port name by selecting *Text* in palette menu, then the *Change value* and *Name Net* box will occur at the left corner of screen.

8. Now to make sure that every device has been wired, you can do that by using check sheet operation. Do this by going to *Check*→*Sheet*→*with defaults* on menu bar. After passing this check, save the sheet.

#### **Preparing Design for Functional Simulation.**

Before running any simulation, the designs need to be prepared for simulation. If you want to simulate by QuickSIm II (digital), you need to type *dsim\_prep filename* in your terminal, e.g.

#### > dsim\_prep ota

In our design, we need to simulate by AccuSim II (analog). It can do by typing *sdl\_prep filename 2.0* in your terminal e.g.

#### > sdl\_prep ota 2.0

then the screen will show as below;

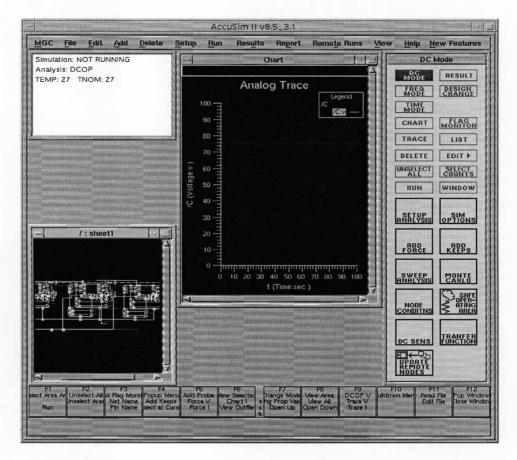

### Simulation with AccuSim II

- Invoke AccuSim II by entering accusim filename/sdl e.g.

> accusim ota/sdl

- Once Accusim is loaded, you should see your schematic. Then, you need to load model for FETs simulation. To load a model file, use *File->Auxiliary Files->Load Model Library* menu. You can enter the filename with your model in it. Use the navigator to load the file that you have created. The model

file (n91wbsim.mod) used in this simulation is based upon a specific MOSIS run named N91W.

3. To see the trace while it is progressing, select voltage or current or port out that want to see output in schematic window. Then click *trace* in palette menu (Figure 3). The graphs will show up with your selected signal in it.

Figure 3. Accusim Window.

4. Set the analysis type by using the Setup Analysis icon. Since you need to perform DC sweep for OTA, you need to press DC sweep button to get the dialog box for setting up the DC sweep. Put the node for sweeping and GND for reference signal. Put range of swept voltage (Figure 4). However, when simulate Chua's circuit, the analysis need to be Transient and the initial voltages have to be set. The initial value can set by clicking button under Use Initial Conditions (-UIC) and click on Setup. Then, the Guess/IC/Nodeset box will show. Select Name button and put node name, voltage and set initial as figure 5.

| Run Mode       | Normal                | Monte Carlo           | Corner Case           |                                                                                                                  |

|----------------|-----------------------|-----------------------|-----------------------|------------------------------------------------------------------------------------------------------------------|

| Analysis       | DCOP                  | DC Sweep              | AC                    | Transient                                                                                                        |

| Time Step*     | [1N                   | Stop Time* 100L       | J                     |                                                                                                                  |

| Time Step used | t if option LVLTIM=3. | Carlos and a Margaret |                       |                                                                                                                  |

| Begin Save     | Time *                | Maximum Ti            | ime Step*             | i i i i i i i i i i i i i i i i i i i                                                                            |

| 🔳 Use Initi    | ial Conditions (- L   | JIC) Setup]           | 11 1 23               | and the second |

| Setup          | Checkpoint files      | Freezepoint file      | Use Restart file      | 6-1-5-1-1-1-                                                                                                     |

| Transie        | nt Noise Analysis     | 197. N 197 7 3        | 17780                 | The Party                                                                                                        |

| Set Run Sy     |                       |                       |                       |                                                                                                                  |

|                |                       |                       | and the second second | and the second                                                                                                   |

| Off Pe         | erform Safe Opera     | ating Area Check Se   | etup                  |                                                                                                                  |

|                | Temperature 27        | Nominal Tempera       | ture 27               |                                                                                                                  |

| Simulation     |                       |                       |                       |                                                                                                                  |

|                | close of the dialo    | g box Use DC          | OP startup file       |                                                                                                                  |

Figure 4. Setup Analysis Window.

- 5. Now click *run* in palette menu to run simulation (figure 3).

- 6. After simulation is complete, if you want to operate trace of signals such as adding two signals or plotting one signal versus the other signal, you click to X-axis of signal trace. Then click the right button of mouse. The menu will pop up. Select *chart* then the chart menu will show up. You can select any operation that you want (Figure 5).

|                                                                                                                | Chart Result        |

|----------------------------------------------------------------------------------------------------------------|---------------------|

| AA A+                                                                                                          | B A-B A*B A/B AvsB  |

| Signel A                                                                                                       | Run Name            |

|                                                                                                                |                     |

| For AC analysis, plot B                                                                                        | ode Mag Phase       |

| the second s |                     |

| Magnitude in dB                                                                                                | Phase in Degrees    |

|                                                                                                                |                     |

| If AvsB plot, only Mag v                                                                                       | s Mag is available. |

|                                                                                                                | s Mag is available. |

| Chart Window New                                                                                               | Selected            |

| Chart Window New<br>Y-AXIS NewStacke                                                                           | ∐ Selected          |

| Chart Window New                                                                                               | Selected            |

| Chart Window New<br>Y-AXIS NewStacke                                                                           | Selected            |

Figure 5. Chart Result Box.

7. Once your simulation is working properly, save your setup for use later. Do this via the *File->Simulation->Save Setup* menu.

Do same procedures with Chua's circuit but use transient analysis and set initial voltage condition for V1, V2, and V3. If you don't set initial condition for voltage, the chaotic signal will never occur.

## Layout

1. Invoke IC Station by entering

> ic &

2. Once the window is shown up, you may need to set up the environment for easier use. Using the *MGC->Setup->Session* menu. You may select Up Down Tiling or Left Right Tiling in Window Layout as show in figure 6. Leave everything else at the default.

|                         | Setup Session         |

|-------------------------|-----------------------|

|                         | Show Menu Bar         |

| elect Input Device:     | Show Session Title    |

|                         | Show Message Area     |

|                         | Show Palette          |

|                         | Show Status Line      |

|                         | Show Softkeys         |

| ouble Click Speed       | Window Layout         |

| > Slow                  | The Stacking          |

| $\diamond$              | Up Down Tiling        |

|                         | 💊 Quadrant Tiling     |

| $\overline{\mathbf{a}}$ | Left Right Tiling     |

| 🔶 Fast                  | Ask User for Position |

| JI Auto                 | Pop Active Window     |

| οκι                     | Reset   Cancel        |

Figure 6. Setup Session Box.

3. Now we need to create new cell. Use the Cell →Create option on the palette menu or use the File →Cell→Create menu to do this. Enter file name in cell name box. Then, select CE (Connectivity editing mode) under Connectivity Mode (Figure 7). This will allow you to keep the connectivity information between your layout and schematic. Select EDDM button under Logic Source type and leave everything else blank.

| Cell Name  | Navigator | Angle Mode<br>Ninety<br>Forty-five<br>All Angle | Connectivity Mode        | Connect by<br>Construction |

|------------|-----------|-------------------------------------------------|--------------------------|----------------------------|

|            | Navigator | Cell Type                                       | Logic Source Type        |                            |

| Process    | Navigator | Standard<br>External<br>Left Cap                | EDDM Schematic Viewpoint | Navigator                  |

| Rules File | Navigator | Via                                             | Logic Loading Optic      |                            |

- Figure 7. Create Cell Window.

- 4. Once the empty cell has been opened, you need to set logic source for your cell. To do this, go to the SDL menu via the SDL button on the palette menu. Under Logic, select Set and enter the schematic name followed by "/sdl" e.g.

*ota/sdl*. You can use navigator to select the viewpoint. Then open the schematic by going to *Open button*. The schematic window will show up. Be sure to select the correct viewpoint for if you don't, the tools will not able to recognize your transistors.

- 5. At this point, you will have two windows. One is a cell that is empty. The other is a logic source that has your schematic design. Now you can place devices in your cell. Before you do that your cell has to be active. If it is not, click on window to make it active. The device can be placed in two different ways. One is Use Diffusion Sharing so that the ICgraph will automatically merge series and parallel transistors. The other is Don't Use Diffusion Sharing that will place transistors individually. For our OTAs and Chua's circuit, we will use Don't Use Diffusion Sharing. Do this by go to MDK menu and select *Don't Use Diffusion Sharing*.

- 6. Now you can place the devices into your cell. To do this, click on *A* Int under the schematic section of the palette menu (Figure 8). At this point, tools will generate the dimension of device based on the width and length parameters specified on the instances and place into the open cell. Overflow lines (in yellow) will show you the connectivity points in your circuit. These overflows will disappear when you have made the correct connection.

| SC       |               |

|----------|---------------|

| Back     | Edit          |

| Legic    |               |

| Set      | Update        |

| Open     | Close         |

| Schem    | 1311          |

| Unhigh   | Filter        |

| S Inst   | S Port        |

| M inst   | M Port        |

| U Inst   | U Port        |

| A Inst   | Cleanup       |

| Setup    |               |

| PortStyl |               |

| Conn     |               |

| SoNet    | SaPort        |

| ResAll   | Ressel        |

| ActNet   | AddNet        |

| ActPort  | AddPort       |

| MakPort  | <b>AmPort</b> |

| Deac     |               |

| Add      |               |

| Dev      | Cell"         |

| Via"     | nvo           |

| Shape"   | Path*         |

| PrpTxt"  | Route         |

| Edit     |               |

| Chg Dev  | Chg Pth       |

| Chg Lyr  | Cpy Lyr       |

| Mak Cel  | Flatten       |

| Flip H   |               |

| Sid Rte  |               |

| Auto     |               |

| AutoR    | Comp          |

Figure 8. SDL Palette Menu.

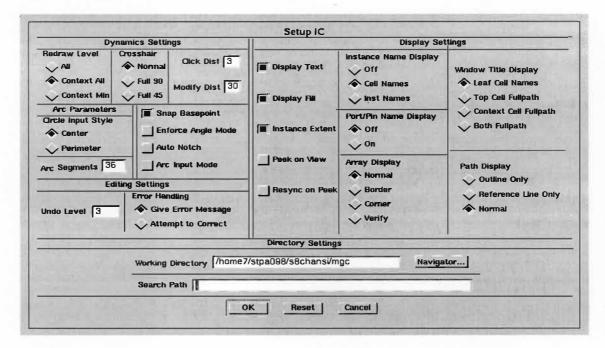

7. Now you can wire up the devices. Between wiring, you may need to undo several times. It is very helpful to change the default undo level (three) to a higher value so you can undo more operations. To do this, go to Setup  $\rightarrow IC$

menu, then change undo level. You may need names of instances while wiring. Do this by turn on name under *Port/Pin Name Display* in Setup IC menu as show in figure 9.

Figure 9. Setup IC Window.

- 8. Since the routes cannot be only one layer, it needs to use different types of layers such as METAL1, METAL2 and POLY. The layer palette will make it easier. To do this, type sho la p (This stands for "show layer palette"). Now you can select layers that need to use for routing. For our design, we need METAL1 and METAL2 for source/drain routing , POLY for gate routing, ELECTRODE for capacitors, VIA for contacting METAL1 and METAL2, CONTACT\_TO\_POLY for contacting POLY and METAL1 and CONTACT\_TO\_ELECTRODE for contacting ELECTRODE and METAL1. The layer palette will show on upper right corner.

- 9. Wiring up devices has many ways. For us, we will use *Path* in the Add menu or under Easy Edit menu. When you click *Path*, then the *ADD PA* box will pop up on bottom left corner. Select the *Option* button to enter width layer as shown in figure 10. Selecting the Keep Option Settings box and exit the dialog box. For our design, we use the width of POLY for 2 micron, of METAL1 for 3 and 4 micron and of METAL2 for 3 and 4 micron. Now you can place layer paths.

Figure 10. Layer Option Box.

- 10. Since the different layer can not connect directly, you need to have special layer to connect such as VIA.

- For connecting METAL1 and METAL2, you need to create 2x2 via, 4x4 METAL1 layer and 4x4 METAL2 layer. Do this by using Shape button in palette menu. The dimension of shape will show on top of cell widow.

- For connecting POLY and METAL1, you need 5x5 POLY layer, 5x5 METAL1 layer and 2x2 POLY\_TO\_CONTACT layer.

- For connecting POLY and METAL2, you need to have METAL1 for connecting because POLY layer can not connect to METAL2 directly. Create 5x5 POLY layer, 2x2 POLY\_TO\_CONTACT layer and 5x5 METAL1 layer. Then routing POLY layer and METAL1 layer to this connection. Next, create 4x4 METAL2, 4x4 METAL1 and 2x2 VIA and route them.

- 11. Once the gates, sources and drains are wired up, you need to place the ports for inputs and outputs from your schematic. Click *PortStly* on the Setup palette menu as shown in figure 8. You should select *Process Port* on the dialog box to display the ports defined for this process (Figure 11)

|                      | Set A          | ctive Por | t Style    |             |    |

|----------------------|----------------|-----------|------------|-------------|----|

| Select Attr          | ibutes Fron    | n         |            | -11577      |    |

| $\hat{\mathbf{v}}$   |                |           |            |             |    |

| Layer                | Process        | Port      |            |             |    |

| Select a Po          | ert Style      |           |            |             |    |

| port (wid            | th = 3)        |           |            |             | 2  |

| default (v           | vidth = 4)     |           |            |             |    |

|                      |                |           |            |             |    |

|                      |                |           |            |             |    |

|                      |                |           |            |             |    |

|                      |                |           |            |             |    |

|                      |                |           |            |             | 17 |

|                      |                |           |            |             |    |

|                      |                |           |            |             |    |

| Routing Le           | Ner META       | L2.POR    | T          |             |    |

|                      | a contraine a  |           |            |             |    |

| Routing Le           | a distanti and |           | T<br>Heigh | <b>r</b> 4  |    |

| Routing Le<br>Previe | a contraine a  |           |            | <b>*</b> [4 | 1  |

|                      | a contraine a  |           | Heigh      | t 4<br>ncel |    |

Figure 11. Set Active Port Style Box.

- 12. We will use METAL2 for ports. Select *the default* line and then click on *Preview* to see its parameters. Notice that it is on METAL2 and it is 4x4 microns as figure 11.

- 13. To place ports, click on *M* Port *I* under Schem menu (Figure 8). All nets with a port are selected and a port shape is created and placed. Then you can are prompted to move these ports to where you want.

- 14. All ports are on METAL2, but the power and ground ports should really be on METAL1. In addition, the size for these ports should be changed so they stretch the full length of the cell.

- a. Change port layer by selecting the VDD and VSS ports and then using the *Objects* -*Change* -*Layer* menu to move them to METAL1.

- b. Resize the ports by *Stretching* them to the desired width and leave them as 4 microns high.

- 15. You need to change the *direction* of all ports that are not inputs. This is because the port placement routine forces all ports to be IN. Power ports you can ignore but for the output, you need to change its direction to OUT. To do

this, use the *Object*  $\rightarrow$ *Change*  $\rightarrow$ *Port* menu to change the direction to OUT and make sure the type is *Signal*. Leave all other items alone. Wire up all ports.

- 16. Now you need to place the diffusion contacts. In MDK package, they have two contact cells. These are available in *\$MGC\_HEP/tutorial/sdl/cells* called nwell\_contact and pwell\_cotact. Get these contacts and abut them to the MOS devices in the layout. Route nwell\_contact with VDD and pwell\_contact with VSS.

- 17. Now the layout needs to check by DRC. To do this, go back to the Session palette and then select *ICrules*. Do a *check* of your circuit and then use the scan menu items to locate the errors. If there are any error, you need to fix all DRC errors before saving cell and going to next step.

### IC Extraction and Backannotation

- 1. Before the extraction can be run, your layout must match your schematic. LVS will check this for you. To do this, you select the *Ictrace (M)* palette menu. This is mask-based LVS checking. It will ignore all hierarchy and look only at the actual connectivity of your devices.

- 2. In the Ictrace menu, select the *LVS* item to bring up LVS dialog box shown in figure 12.

| Report Name Ivs.rep         | Write Database Yes No          |

|-----------------------------|--------------------------------|

| Navigator]                  | File Name maskdb               |

| Source Name                 | Enable Location Probing Yes No |

| Navigator                   | Load Database Yes No           |

| Source Type                 |                                |

| ddm erel spice cnet         | Setup LVS                      |

| bort on Supply Error Yes No | Setup Trace Props              |

|                             | Reset Cancel                   |

Figure 12. LVS Mark Box.

- 3. You will need to supply the schematic source name. Use navigator or type in the source name including the viewpoint. If you use the wrong viewpoint, LVS will fail.

- 4. Then, press the *Setup LVS* button to setup the LVS procedure. The dialog box will be brought up. Leave everything alone except you need to turn the *Recognize Gates* option off. If you do not, then LVS will try to combine transistors into gates and then try to match those gates up against similar gates in your schematic.

- 5. Press OK for Setup dialog box and the LVS dialog box and then LVS will begin. When LVS is complete, you should look at the report by using Report→LVS item from the LVS palette. A text window will appear displaying the report. Be sure is compared correctly. If it did not, you will need to fix any errors before extraction will work.

- 6. Once the layout pass LVS, the layout is ready to backannotated parasitic for simulation. We need to do lumped extraction. Lumped extraction will treat each distinct net as one lumped capacitor and/or resistor. Every point on the net will see the full extracted RC delays, therefore. Hence, a transmission line will look the same so matter where you are on that transmission line.

- 7. To prepare for extraction, be sure your cell is reserved for edit, Go to *ICextract (M)* palette menu. Select *Lumped* from the palette menu to display the extraction dialog box shown in figure 13.

| Write Database Yes N                                                  | 9pecify Scher | Specify Schematic Source Yes No     Source Type |                                |    |  |

|-----------------------------------------------------------------------|---------------|-------------------------------------------------|--------------------------------|----|--|

| August Designation of Bard Commission                                 |               | - Source Name ddm                               |                                |    |  |

| Lumped Resistance? Set Coupled C<br>Set Coupled C<br>Vas No<br>Yas No | ap Threshold? | LVS Report Name [Ivs.rep                        |                                |    |  |

|                                                                       | Setup LVS     | .] Setup Trace Props.                           | Abort on Supply Error Ves      | No |  |

| Update Port Properties<br>Ves No                                      |               | BackAnnotate Yes No<br>BA Name<br>ASCII BA Name |                                |    |  |

| Export File Name                                                      |               | apacitance                                      | esistance Coupling Capacitance |    |  |

Figure 13. Extract Mask Lumped Parameters Box.

- 8. Click *Yes* to the right of the *Specify Schematic Source* to show schematic source. Enter the source name followed by "/sdl" e.g ota/sdl.

- 9. Click on the Setup LVS...button and check to be sure that the recognize gates option is set to *NO*. Accept this box.

- 10. Select YES in the BackAnnotate option for backannotation results.

- 11. Specify the name of a BA file to use. If you choose a previously used name, then you should also select the *YES* button under the Clear option to remove any previous annotation.

- 12. Now select the parameters to backannotated. Accusim will use the *cpl\_cap\_net* property for net capacitance between node and any others. To do this, select *Yes* button under *Coupling Capacitance*. The lumped capacitance can also be used but only you are using GND as opposed to VSS and you change the property name to *cap\_net* form the default *icap\_net*. For our backannotaion, we don't need to use lumped capacitance. So, select *No* button. In addition, Lumped resistance is not used in Accusim.

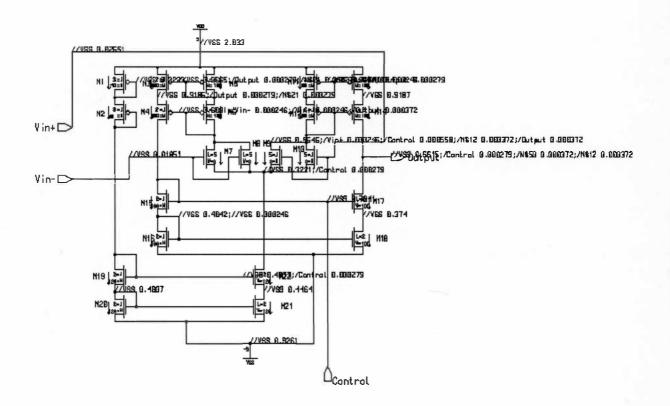

- 13. Accept this dialog box and extract will begin. When the extract is done, you will see that your schematic is automatically updated and you will see annotations (red number) on it as shown in figure 14.

Figure 14. Schematic with Extracted Parasitic. **Post Layout Simulation**

- 1. You can do post simulation the same when your do simulation using Accusim. Type file name to start Accusim e.g. accusim ota/sdl. This will load your schematic with the backannotated lumped resistance and capacitance.

- 2. You can do the set up in Accuim the same as you did before and see the result. The result should not look much different that your functional simulation because there is not much added capacitance nor resistance the layout.

# DRC Report for Chua's Circuit.

|                                                                                | RESULTS<br>IG CURR SCAN          |                                                                                                                               |

|--------------------------------------------------------------------------------|----------------------------------|-------------------------------------------------------------------------------------------------------------------------------|

| bad_active_area                                                                | 0 0 0<br>mgc_libs/gen_lib/       | Rule File Pathname:<br>'mgc_hep/technology/ic/scmos.rules<br>Active area must be covered by a select                          |

| Oct 20 02:37:37 1999<br>CONTACT_TO_POLY, and META                              | 0 0 0<br>mgc_libs/gen_lib/<br>Ll | Rule File Pathname:<br>mgc_hep/technology/ic/scmos.rules<br>Contact to poly must consist of poly,                             |

| /home3/software/mentorgr/<br>Oct 20 02:37:37 1999<br>ELECTRODE, CONTACT_TO_ELE | 0 0 0<br>mgc_libs/gen_lib/       | Rule File Pathname:<br>mgc_hep/technology/ic/scmos.rules<br>Contact to ELECTRODE must consist of<br>J                         |

| Oct 20 02:37:37 1999<br>CONTACT_TO_ACTIVE, and ME                              | mgc_libs/gen_lib/<br>TAL1        | Rule File Pathname:<br>'mgc_hep/technology/ic/scmos.rules<br>Contact to active must consist of active,                        |

| bad_contact_gate<br>/home3/software/mentorgr/<br>Oct 20 02:37:37 1999          | 0 0 0<br>mgc_libs/gen_lib/       | Rule File Pathname:<br>'mgc_hep/technology/ic/scmos.rules<br>Contact to poly may not be on gate region.                       |

| bad_via                                                                        | 0 0 0<br>mgc libs/gen lib/       | Rule File Pathname:<br>'mgc_hep/technology/ic/scmos.rules<br>Via must consist of METAL1, via, and METAL2                      |

| bad_contact_via                                                                | 0 0 0<br>mgc_libs/gen_lib/       | Rule File Pathname:<br>'mgc_hep/technology/ic/scmos.rules<br>Via must NOT be stacked with contact                             |

| select_overlap                                                                 | 0 0 0<br>mgc_libs/gen_lib/       | Rule File Pathname:<br>mgc_hep/technology/ic/scmos.rules<br>Overlap of N+ and P+ not allowed                                  |

| bad_nwell                                                                      | 0 0 0<br>mgc_libs/gen_lib/       | Rule File Pathname:<br>mgc_hep/technology/ic/scmos.rules<br>Nwell must have well contact                                      |

| bad_psubstrate                                                                 | 0 0 0<br>mgc_libs/gen_lib/       | Rule File Pathname:<br>'mgc_hep/technology/ic/scmos.rules<br>Psubstrate must have a substrate contact                         |

| bad_pgate<br>/home3/software/mentorgr/<br>Oct 20 02:37:38 1999                 | mgc_libs/gen_lib/                | Rule File Pathname:<br>'mgc_hep/technology/ic/scmos.rules<br>P-type gate must not be in psubstrate                            |

| bad_ngate<br>/home3/software/mentorgr/<br>Oct 20 02:37:38 1999                 | 0 0 0<br>mgc_libs/gen_lib/       | Rule File Pathname:<br>'mgc_hep/technology/ic/scmos.rules<br>N-type gate must not be in nwell                                 |

| DRC1_1<br>/home3/software/mentorgr/                                            | 0 0 0<br>mgc_libs/gen_lib/       | Rule File Pathname:<br>/mgc_hep/technology/ic/scmos.rules<br>N-Well width = 10L                                               |

| DRC1_2                                                                         | 0 0 0                            | Rule File Pathname:<br>/mgc_hep/technology/ic/scmos.rules<br>N-well spacing (different potential) = 9L<br>Rule File Pathname: |

|                                                                                | mgc_libs/gen_lib/                | Rule File Pathname:<br>'mgc_hep/technology/ic/scmos.rules<br>Active area width = 3L                                           |